DDR5 内存在几个月前才成为主流,但三星已经处于下一代 DDR6 内存的早期开发过程中。

在韩国水原举行的一次研讨会上,三星测试和系统封装 (TSP) 副总裁透露,随着未来内存本身性能的扩展,封装技术需要不断发展。该公司证实,他们已经投入下一代 DDR6 内存的早期开发阶段,该内存将使用 MSAP 技术。

据三星称,MSAP 已被其竞争对手(SK 海力士和美光)用于 DDR5。那么 MSAP 有什么新功能呢?嗯,MSAP 或改进的半加法工艺允许 DRAM 制造商创建具有更精细电路的内存模块。这是通过在先前未触及的空白空间中涂覆电路图案来实现的,从而实现更好的连接和更快的传输速度。下一代 DDR6 内存不仅将利用 MSAP 来增强电路连接,还可以适应将被合并到 DDR6 内存中的层数增加。

相关媒体报道指出,之前的tenting方法只在圆形铜板将要形成电路图案的区域进行涂覆,而将其他区域蚀刻掉。

但在 MSAP 中,除了电路之外的区域都经过涂层处理,而空白区域则进行了电镀,从而可以实现更精细的电路。三星副总裁说,随着存储芯片容量和数据处理速度的增加,封装的设计必须适应这一点。Ko说,随着层数的增加和工艺变得更加复杂,内存封装市场也有望成倍增长。

在扇出方面,另一种将 I/O 端子置于芯片外部以使芯片变得更小同时保持球布局的另一种封装技术,三星同时应用了扇出晶圆级封装 (FO-WLP) 和风扇面板级封装 (FO-PLP)。

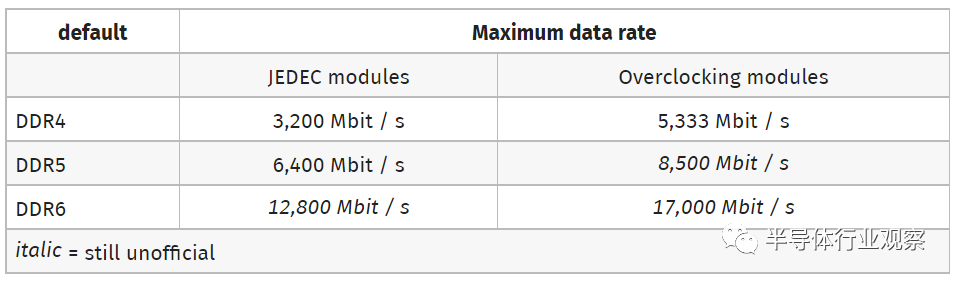

三星预计其 DDR6 设计将在 2024 年完成,但预计 2025 年之后不会商用。在规格方面,DDR6 内存将是现有 DDR5 内存的两倍,传输速度高达 12,800 Mbps(JEDEC ) 和超频速度超过 17,000 Mbps 范围。目前,三星最快的 DDR5 DIMM具有高达 7,200 Mbps 的传输速度,因此在 JEDEC 上提高了 1.7 倍,在下一代内存芯片的超频速度下提高了 2.36 倍。至于每个模块的内存通道数量,DDR6 也将增加一倍,四个 16 位通道由 64 个内存库连接。

至于标准方面,三星表示,DDR6 标准的开发已经开始,并将得到 JEDEC 的协助,JEDEC 是一个由 300 多名成员组成的半导体工程组织,其中包括一些世界上最大的计算机公司。

话虽如此,内存制造商已经强调了在未来将高达 DDR5-12600 的速度,因此 DDR5 绝对具有消费平台的潜力。随着 AMD 的 Zen 4 和英特尔的 Raptor Lake CPU 平台的推出,预计今年晚些时候 DDR5 内存模块会更快、更优化。

Samsung 还透露了一些关于GDDR6 标准的后续资讯,该公司可能正在开发GDDR6+ 标准,提供高达24 Gbps 的速度,比目前GDDR6 标准提供的18 Gbps 更快,GDDR6+ 将使用Samsung 1z nm 制程制造。

根据之前的报道GDDR7 标准也在Samsung 的路线图上,GDDR7 主要将记忆体频宽增加到32 Gbps,并加入即时错误保护功能,不过Samsung 没有提供近一步的技术资料与路线图时间。另外,Samsung 将会在2022 年第二季开始大量生产HBM3 (High-Bandwidth-Memory Gen3) 记忆体。

虽然上述记忆体技术距离实际应用到产品上并且公开贩售仍需要一段时间,不过时代总会不断向前进,科技也是,希望科技发展的同时也能兼顾平价,先讲求不伤荷包,再求速度。

关于DDR 6,我们可能面临的挑战

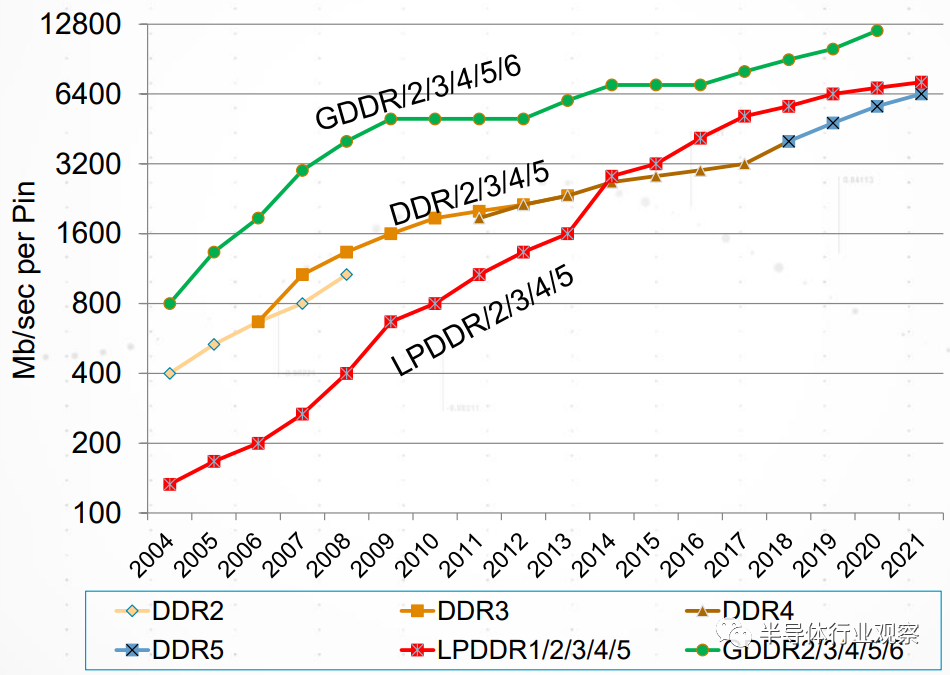

DDR 的引入可以说是电子行业进入高速数字化的时期。当然,ECL 逻辑组件发挥了作用,但 DDR 存储器一直是一个典型的例子,表明数据速率随着时间的推移而稳步提高。DDR5 的应用仍在推进中,但业界已经在展望 DDR6 RAM。这让我想到了应用研究人员在电信中所扮演的基本角色,在 5G 部署完成之前,工程师已经在为 6G 进行开发。

在 DDR3 之前,设计人员需要考虑设计以适应建立和保持时间以及总线上的受控阻抗。直到 DDR3 数据速率的高端为止,色散补偿都不是这样的问题,因为抖动开始成为信号解释中的主要问题。在低电平信号中看到的相对较小的抖动将大到足以关闭 DDR3 信号的眼图。因此,更新了 JEDEC 标准以提供 DDR4 眼图的设计容差。

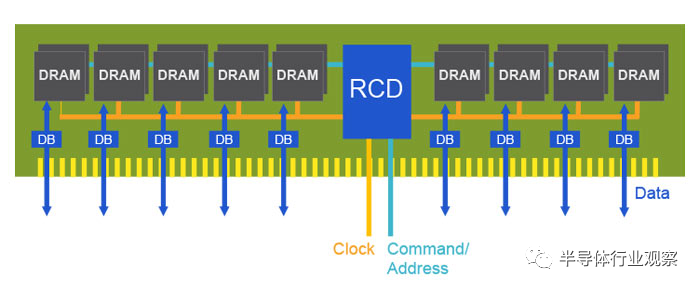

DDR5 采用了高端 DDR4 数据速率,并通过使总线更快而不是更宽而再次将其翻倍。在布置并行单端网络方面,您仍在处理 DDR4 布线挑战,但这些通道要短得多。总线也将运行得足够快,以至于误码主要由接收器处的反射损耗、任何层转换处以及色散引起。较短的通道有效地降低了总插入损耗,但回波损耗色散 需要通过极高带宽的极其精确的互连阻抗设计来补偿。

对于 DDR5,数据传输在具有双向通信的单端网络上以短脉冲形式发生。全速时钟允许在互连的每一端在读取和写入之间切换。一切都必须非常快速地切换,这需要无可挑剔的 PDN 设计来尽可能地抑制抖动。典型电路板上的 PDN 阻抗只能变得如此之低,而且 DDR5 中的低信号电平(最大 1.1 V)对数字信号施加了非常严格的纹波/抖动限制。这些以反射为主的通道问题和叠加在低电平信号上的低纹波要求现在迫使控制器在 DDR5 接口中使用均衡,以补偿信号失真和符号间干扰 (ISI)。请注意,这种均衡已经用于高速差分串行标准(例如,SerDes 通道中的 LVDS)。

DDR5 中还有许多其他设计挑战需要考虑,但上面列出的挑战可以说是最大的挑战。

那么DDR6内存呢?

与前几代产品一样,DDR6 RAM 旨在将 DDR5 的最大数据速率提高一倍。如果您正在为 DDR6 RAM 创新模块,仍然有很多未解决的问题。人们普遍认为总线不会更宽,而且 DDR5 的速度已经快到足以撞上所谓的“内存墙”。这使得调制(例如 PAM 或 QAM)成为提高数据速率超过完全模拟通道(例如 100G 以太网)的最后可用选项。

由于进入模拟高速通道会破坏我们对 DDR 的了解,您可能会看到 PAM 或 QAM 与控制器中嵌入的一些专有均衡方案相结合。虽然主要挑战在于 IC 设计人员,但当我们查看 DDR6 RAM 通道中使用的高带宽信号时,电路板设计人员仍有许多需要解决的问题。

DDR6 RAM 中的挑战主要发生在芯片级,但 DDR5 中相同的板级挑战也适用于 DDR6 RAM。我上面提到的 DDR5 中的电源完整性挑战不会在 DDR6 RAM 中消失。一旦对 DDR6 信号施加调制,DDR6 的电源完整性挑战就是将平坦的 PDN 阻抗扩展到更高的信号带宽。将平坦的 PDN 阻抗扩展到更高的频率就是要使 Tx 侧的抖动保持在较低水平,从而使 Rx 侧的 ISI 保持足够低,以便可以通过均衡来解析信号。DDR5 模块的板载电源管理 IC 可能还会出现在 DDR6 RAM 模块上,以帮助调节整个模块的电源。

嵌入式系统设计人员可能会落后于 DDR5/6 用户。与使用模块(PC 和服务器)的系统相比,它们将拥有更轻松的时间,因为连接器处的损耗被消除并转移到球/模具级别。然而,更小的空间对于嵌入式设计师来说是一把双刃剑。这些系统更小,因此他们已经希望将内存 IC 安装在靠近系统控制器的板上。然而,由于空间更小,他们现在更难以处理电路板部分之间的辐射 EMI。

像在不同功能块之间进行屏蔽这样简单的东西对于嵌入式和 PC/服务器都是有用的。在这里,我们正在讨论两种可能的屏蔽类型:

高带宽隔离结构。可以调整这些结构以提供高达高频的高隔离度。它们占据了表层的空间,但这些结构比调谐到更高频率时变得更小。这是嵌入式系统的一个选项,其中 RAM IC 与控制器放置在同一块板上。

不同层的创意路由。您可以利用内部平面来防止主板上不同 DDR 总线之间的串扰。一旦你突破了模块的连接器,模块可能与其他电路足够远,串扰不再是问题。